メッセージ

当研究室を志望される学生の方へ

研究内容

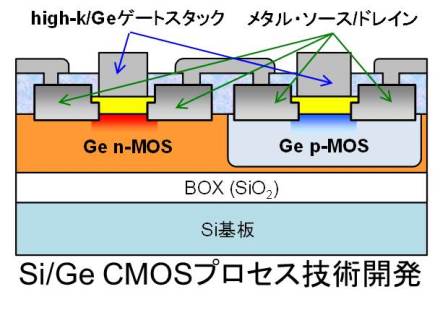

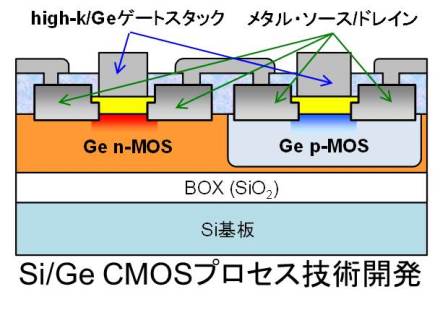

Si/Ge CMOSプロセス技術

CMOS(相補型MOSトランジスタ)は、ULSIの基本構成デバイスで、微細化により高性能化(高速・低消費電力化)を達成してきました。しかし、Si材料物性の制約から、微細化だけではその性能向上が実現できない時代に突入しています。そのため、ブースター技術と呼ばれる研究開発が不可欠となっています。それらの技術とは、(1) 高誘電率ゲートスタックの開発、(2) 高移動度チャネル材料の開発、(3) ソース・ドレインの寄生抵抗の低減、等です。中島研究室では、これらの課題に真正面から取り組んでいます。キーワードは、高品質ゲートスタックの低温形成、Geチャネル、歪み、SOI(GOI)、金属ソース・ドレイン、等です。

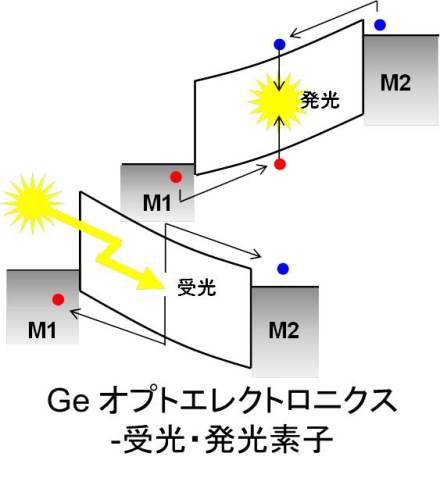

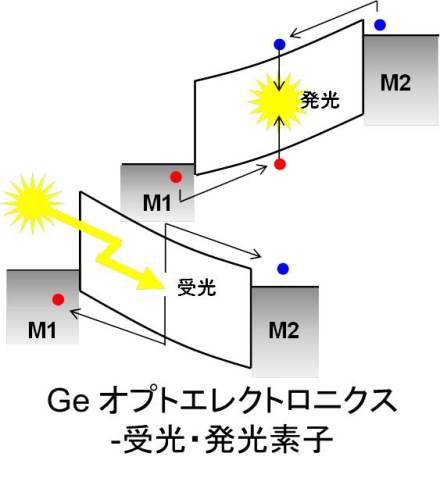

Geオプトエレクトロニクス

Geは次世代CMOSのチャネル候補材料で、電子・正孔の移動度はSiに比べて格段に大きい特徴を持ちます。更に、Geの直接遷移禁制帯幅は0.80 eVで、光通信波長帯(波長1.55 μm)と良く一致します。従って、Geに受光・発光機能が賦与できれば、Ge-CMOSと混載可能な光素子への道が拓かれ、素子間の光接続等の広範囲な応用が期待できます、中島研究室は、Geプロセスに関して多くの独自技術を保有しており、これらを活用したGe-受光・発光デバイスの研究を開始しています。

SiCプロセス技術(エア・ウォーター株式会社との共同研究)

4H-SiCやGaN等のワイドギャップ半導体は、パワーデバイスの基板材料として注目されています。一方、ワイドギャップ半導体の別の利点は高温(200~250℃)動作です。高温動作可能なCMOSがエンジン周りに配置できれば、コンパクト化、配線の簡素化、ノイズ対策の不用化、等の利点が生ずるはずです。中島研究室では、その材料として、3C-SiC(禁制帯幅:2.2 eV)に着目しています。その利点は、(1) Si基板上にエピタキシャル成長すること、(2) 電子のチャネル移動度が高いこと、(3) Siテクノロジーがそのまま使えること、等です。3C-SiCのプロセス技術の研究を実施しています。

Si/Ge CMOSプロセス技術

CMOS(相補型MOSトランジスタ)は、ULSIの基本構成デバイスで、微細化により高性能化(高速・低消費電力化)を達成してきました。しかし、Si材料物性の制約から、微細化だけではその性能向上が実現できない時代に突入しています。そのため、ブースター技術と呼ばれる研究開発が不可欠となっています。それらの技術とは、(1) 高誘電率ゲートスタックの開発、(2) 高移動度チャネル材料の開発、(3) ソース・ドレインの寄生抵抗の低減、等です。中島研究室では、これらの課題に真正面から取り組んでいます。キーワードは、高品質ゲートスタックの低温形成、Geチャネル、歪み、SOI(GOI)、金属ソース・ドレイン、等です。

Geオプトエレクトロニクス

Geは次世代CMOSのチャネル候補材料で、電子・正孔の移動度はSiに比べて格段に大きい特徴を持ちます。更に、Geの直接遷移禁制帯幅は0.80 eVで、光通信波長帯(波長1.55 μm)と良く一致します。従って、Geに受光・発光機能が賦与できれば、Ge-CMOSと混載可能な光素子への道が拓かれ、素子間の光接続等の広範囲な応用が期待できます、中島研究室は、Geプロセスに関して多くの独自技術を保有しており、これらを活用したGe-受光・発光デバイスの研究を開始しています。

SiCプロセス技術(エア・ウォーター株式会社との共同研究)

4H-SiCやGaN等のワイドギャップ半導体は、パワーデバイスの基板材料として注目されています。一方、ワイドギャップ半導体の別の利点は高温(200~250℃)動作です。高温動作可能なCMOSがエンジン周りに配置できれば、コンパクト化、配線の簡素化、ノイズ対策の不用化、等の利点が生ずるはずです。中島研究室では、その材料として、3C-SiC(禁制帯幅:2.2 eV)に着目しています。その利点は、(1) Si基板上にエピタキシャル成長すること、(2) 電子のチャネル移動度が高いこと、(3) Siテクノロジーがそのまま使えること、等です。3C-SiCのプロセス技術の研究を実施しています。

Japanese

Japanese English

English